數(shù)字集成電路物理設(shè)計(jì) 從理論到實(shí)現(xiàn)的全流程解析

數(shù)字集成電路物理設(shè)計(jì)是芯片從邏輯概念走向硅片實(shí)現(xiàn)的關(guān)鍵階段,它直接決定了芯片的性能、功耗、可靠性和制造成本。隨著工藝節(jié)點(diǎn)不斷微縮,物理設(shè)計(jì)的復(fù)雜性日益增加,掌握其核心流程與工具已成為集成電路設(shè)計(jì)工程師的必備技能。

一、物理設(shè)計(jì)的基本概念與重要性

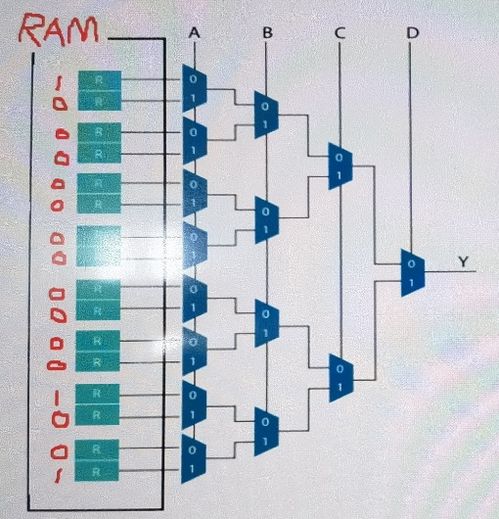

物理設(shè)計(jì)(Physical Design)又稱后端設(shè)計(jì),主要任務(wù)是將邏輯綜合后的門(mén)級(jí)網(wǎng)表轉(zhuǎn)換為可供制造的版圖(Layout)。這一過(guò)程涉及布局規(guī)劃、時(shí)鐘樹(shù)綜合、布線、時(shí)序收斂、功耗優(yōu)化和物理驗(yàn)證等多個(gè)環(huán)節(jié)。在納米級(jí)工藝下,互連線延遲已超過(guò)門(mén)延遲成為主導(dǎo),物理設(shè)計(jì)對(duì)芯片最終性能的影響至關(guān)重要,任何疏漏都可能導(dǎo)致流片失敗。

二、物理設(shè)計(jì)的主要流程詳解

- 數(shù)據(jù)準(zhǔn)備與庫(kù)文件導(dǎo)入:設(shè)計(jì)始于工藝廠商提供的標(biāo)準(zhǔn)單元庫(kù)、IO庫(kù)和物理庫(kù),以及邏輯綜合后的門(mén)級(jí)網(wǎng)表與時(shí)序約束文件。

- 布局規(guī)劃(Floorplanning):確定芯片大小、模塊位置、電源網(wǎng)絡(luò)結(jié)構(gòu)和IO引腳排列。良好的布局規(guī)劃能優(yōu)化布線擁塞、降低互連延遲并提高面積利用率。

- 電源規(guī)劃(Power Planning):設(shè)計(jì)全局和局部電源網(wǎng)絡(luò),確保供電均勻穩(wěn)定,避免IR壓降和電遷移問(wèn)題。

- 單元放置(Placement):將標(biāo)準(zhǔn)單元放置在芯片布局區(qū)域內(nèi),優(yōu)化線長(zhǎng)、時(shí)序和功耗。現(xiàn)代工具常采用時(shí)序驅(qū)動(dòng)的放置算法。

- 時(shí)鐘樹(shù)綜合(Clock Tree Synthesis, CTS):構(gòu)建低偏斜、低功耗的時(shí)鐘分布網(wǎng)絡(luò),確保時(shí)鐘信號(hào)同步到達(dá)所有時(shí)序單元。

- 布線(Routing):完成單元間的物理連接,分為全局布線和詳細(xì)布線兩步。需考慮信號(hào)完整性、串?dāng)_和金屬層利用率。

- 時(shí)序收斂與優(yōu)化:通過(guò)插入緩沖器、調(diào)整單元尺寸或重新布線等手段,滿足建立時(shí)間和保持時(shí)間要求。

- 物理驗(yàn)證:包括設(shè)計(jì)規(guī)則檢查(DRC)、版圖與電路圖一致性檢查(LVS)和電氣規(guī)則檢查(ERC),確保版圖符合制造要求。

三、主流EDA工具與資源獲取

業(yè)界廣泛使用的物理設(shè)計(jì)工具包括Cadence Innovus、Synopsys IC Compiler II和Mentor Tessent等。對(duì)于學(xué)習(xí)和研究,部分工具提供教育版本或開(kāi)源替代方案(如OpenROAD)。

關(guān)于PPT等學(xué)習(xí)資源的獲取,建議通過(guò)以下途徑:

- 訪問(wèn)EDA廠商官方網(wǎng)站的技術(shù)文檔和培訓(xùn)材料專區(qū)

- 關(guān)注知名大學(xué)(如MIT、斯坦福、UC Berkeley)集成電路課程公開(kāi)課件

- 查閱IEEE/ACM等學(xué)術(shù)會(huì)議論文集及相關(guān)講座錄像

- 加入專業(yè)論壇(如EDACN、EETOP)獲取行業(yè)分享資料

四、物理設(shè)計(jì)的發(fā)展趨勢(shì)與挑戰(zhàn)

隨著工藝進(jìn)入5納米及以下節(jié)點(diǎn),物理設(shè)計(jì)面臨諸多新挑戰(zhàn):

- 三維集成電路與先進(jìn)封裝技術(shù)的應(yīng)用

- 多物理場(chǎng)耦合效應(yīng)(熱電機(jī)械)的協(xié)同優(yōu)化

- 機(jī)器學(xué)習(xí)在布局布線算法中的深度融合

- 可制造性設(shè)計(jì)(DFM)與良率提升的閉環(huán)優(yōu)化

數(shù)字集成電路物理設(shè)計(jì)是藝術(shù)與科學(xué)的結(jié)合,工程師需在約束條件中尋找最優(yōu)解。系統(tǒng)學(xué)習(xí)理論知識(shí)、熟練使用EDA工具、關(guān)注業(yè)界動(dòng)態(tài)并參與實(shí)際項(xiàng)目,是掌握這一關(guān)鍵技能的必由之路。不斷更新的技術(shù)文檔與培訓(xùn)資源,將為從業(yè)者提供持續(xù)學(xué)習(xí)的寶貴支持。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.jzjsh.cn/product/19.html

更新時(shí)間:2026-03-09 20:53:27